一、移位器

| 控制位 |

工作方式 |

| 000 |

清零 |

| 001 |

置数 |

| 010 |

逻辑右移 |

| 011 |

逻辑左移 |

| 100 |

算数右移 |

| 101 |

左端串行输入1位值,并行输出8位值 |

| 110 |

循环右移 |

| 111 |

循环左移 |

以下是一个移位寄存器的实现:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

| module move(ctl,out,clk,in,in1);

input wire clk;

input wire [7:0] in;

input reg[2:0] ctl;

input wire in1;

output reg [7:0] out;

reg temp_reg;

always @(clk) begin

case(ctl)

3'b000:

out <= 8'b0000_0000;

3'b001:

out <= in;

3'b010:

out <= {1'b0,out[7:1]};

3'b011:

out <= {out[6:0],1'b0};

3'b100:

out <= {out[7],out[7:1]};

3'b101:

out <= {in1,out[6:0]};

3'b110:

out <= {out[0],out[7:1]};

3'b111:

out <= {out[6:0],out[7]};

default:

out <=8'b0000_0000;

endcase

end

endmodule;

|

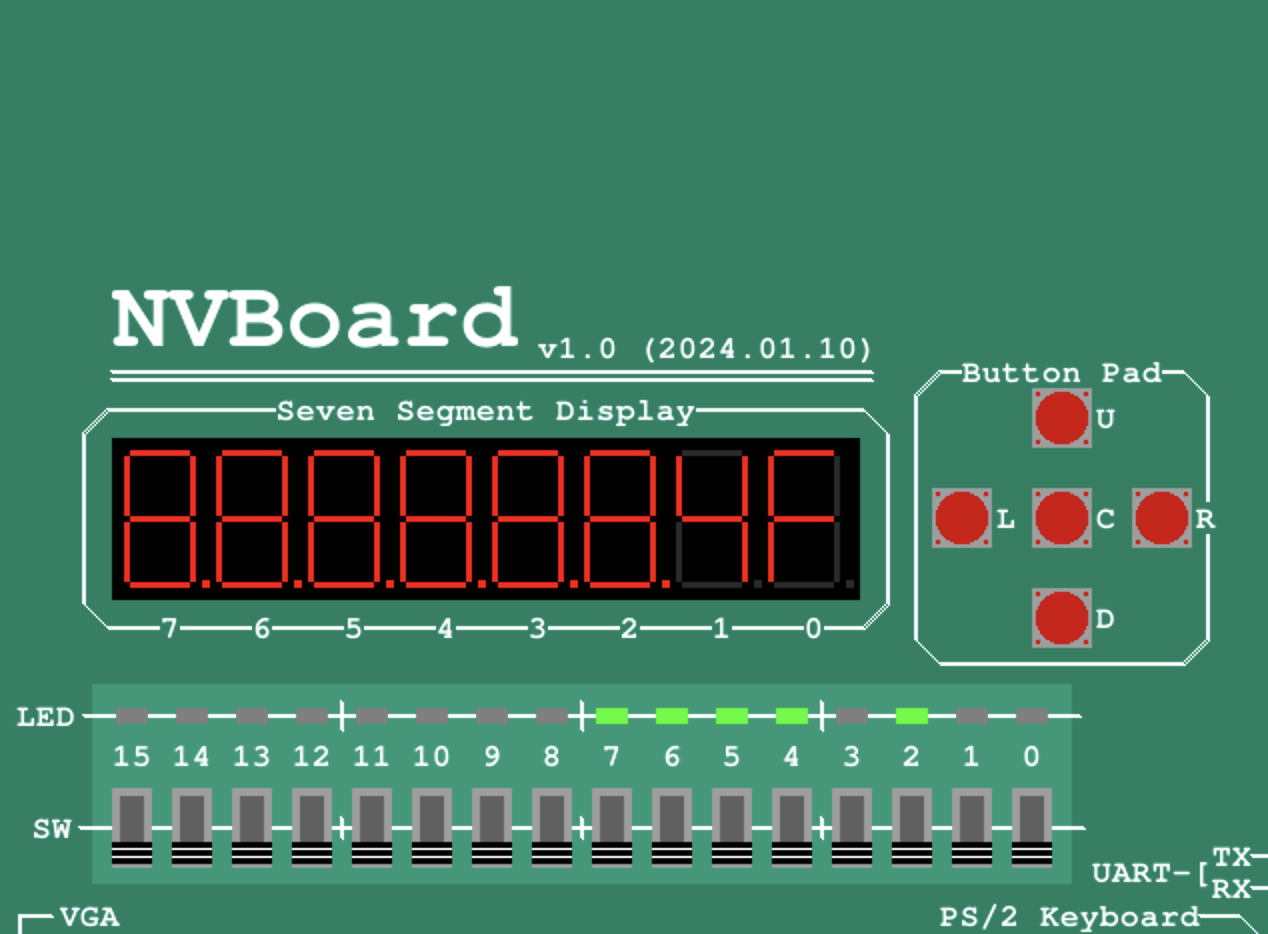

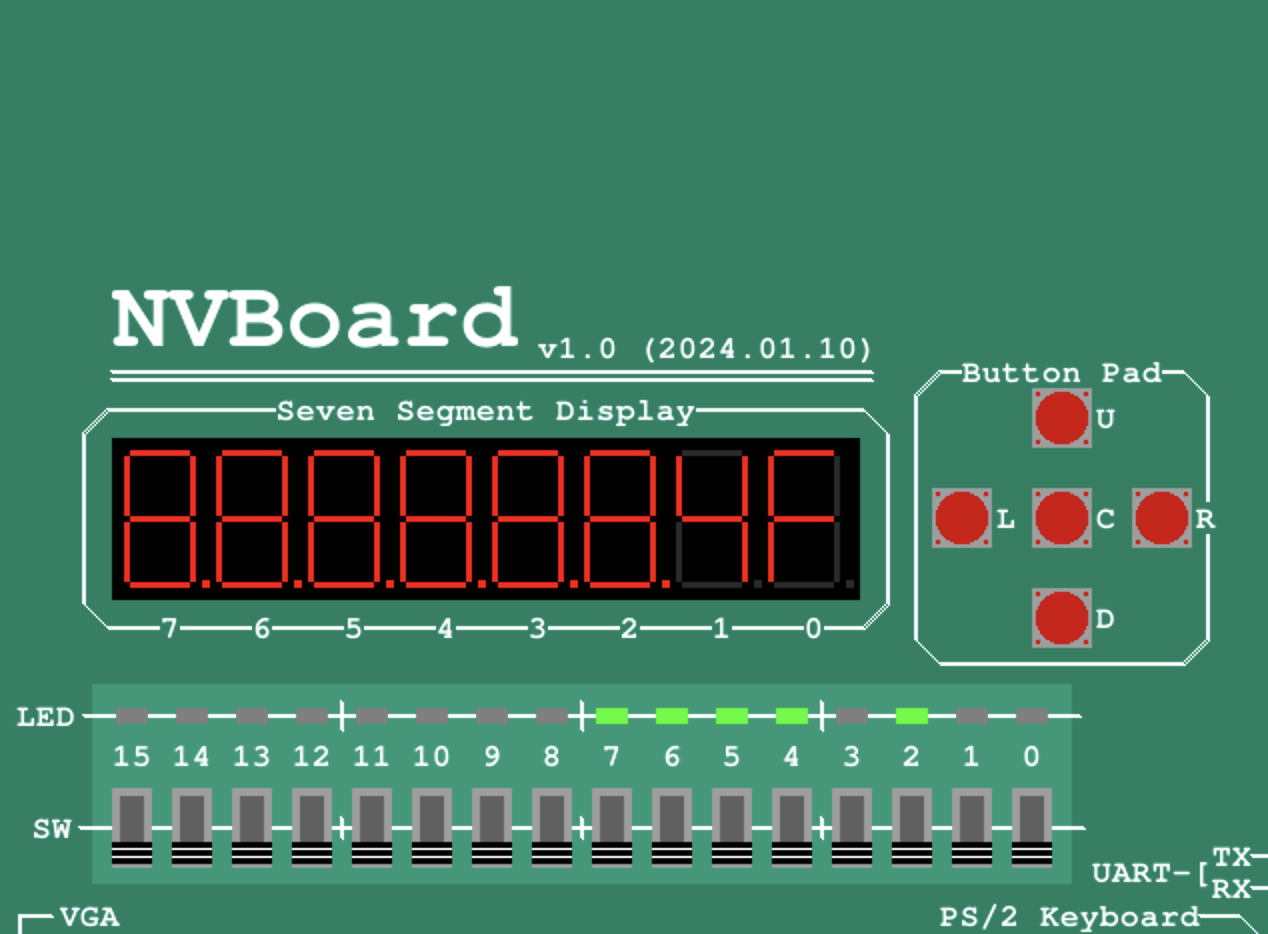

仿真结果

二、实验

请实现一个8位的周期为255的伪随机序列,以按钮为时钟信号,并请将8位二进制数以十六进制显示在数码管上:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

| module LFSR8(

input wire clk,

input wire reset,

input wire enable,

output reg [7:0] out,

output reg [7:0] bcd7seg,

output reg [7:0] bcd7seg2

);

reg new_bit;

initial

out = 8'b00000001;

always @(reset or enable) begin

if (reset) begin

out <= 8'b00000001;

end

else if (enable) begin

new_bit <= out[4] ^ out[2] ^ out[1] ^ out[0];

out <= {new_bit, out[7:1]};

end

case(out[7:4])

4'b0000:

bcd7seg = ~8'b11111101;

4'b0001:

bcd7seg = ~8'b01100000;

4'b0010:

bcd7seg = ~8'b11011010;

4'b0011:

bcd7seg = ~8'b11110010;

4'b0100:

bcd7seg = ~8'b01100110;

4'b0101:

bcd7seg = ~8'b10110110;

4'b0110:

bcd7seg = ~8'b10111110;

4'b0111:

bcd7seg = ~8'b11100000;

4'b1000:

bcd7seg = ~8'b11111110;

4'b1001:

bcd7seg = ~8'b11100110;

4'b1010:

bcd7seg = ~8'b11101110;

4'b1011:

bcd7seg = ~8'b00111110;

4'b1100:

bcd7seg = ~8'b10011100;

4'b1101:

bcd7seg = ~8'b01111010;

4'b1110:

bcd7seg = ~8'b10011110;

4'b1111:

bcd7seg = ~8'b10001110;

default:

bcd7seg = ~8'b10001110;

endcase

case(out[3:0])

4'b0000:

bcd7seg2 = ~8'b11111101;

4'b0001:

bcd7seg2 = ~8'b01100000;

4'b0010:

bcd7seg2 = ~8'b11011010;

4'b0011:

bcd7seg2 = ~8'b11110010;

4'b0100:

bcd7seg2 = ~8'b01100110;

4'b0101:

bcd7seg2 = ~8'b10110110;

4'b0110:

bcd7seg2 = ~8'b10111110;

4'b0111:

bcd7seg2 = ~8'b11100000;

4'b1000:

bcd7seg2 = ~8'b11111110;

4'b1001:

bcd7seg2 = ~8'b11100110;

4'b1010:

bcd7seg2 = ~8'b11101110;

4'b1011:

bcd7seg2 = ~8'b00111110;

4'b1100:

bcd7seg2 = ~8'b10011100;

4'b1101:

bcd7seg2 = ~8'b01111010;

4'b1110:

bcd7seg2 = ~8'b10011110;

4'b1111:

bcd7seg2 = ~8'b10001110;

default:

bcd7seg2 = ~8'b10001110;

endcase

end

endmodule

|

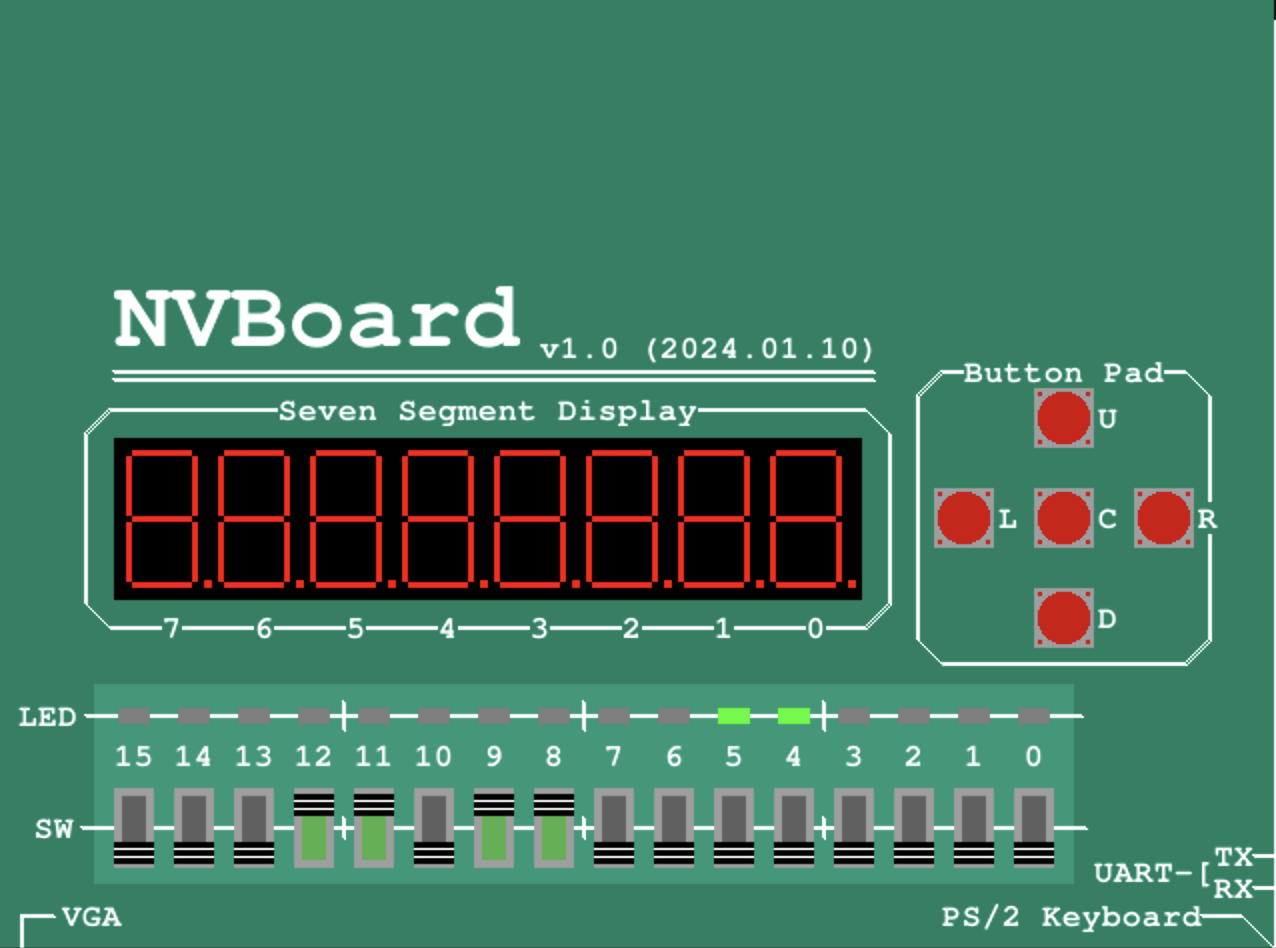

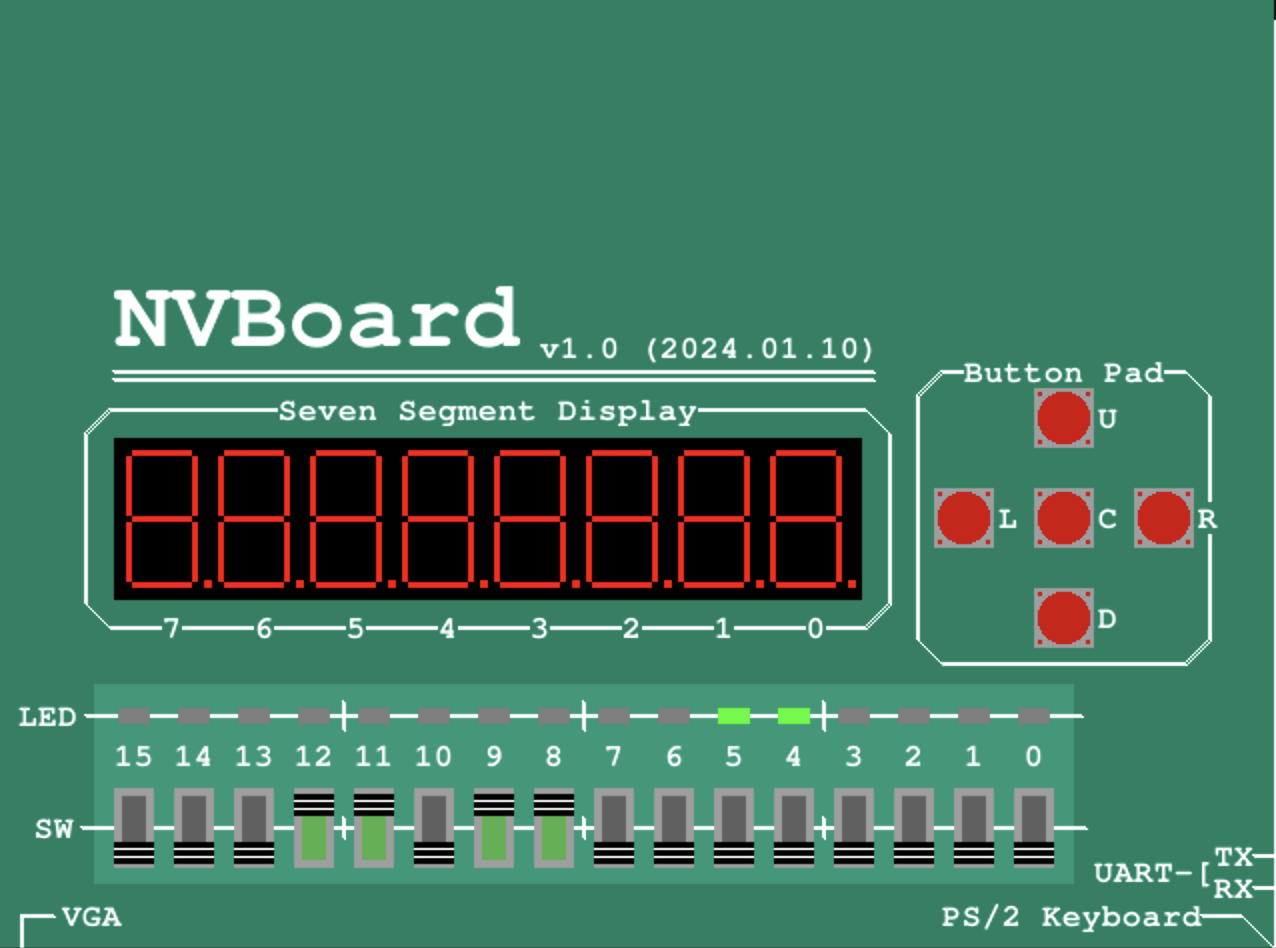

仿真结果